# Connor Sorrell—Lab 15 Ecen 3730

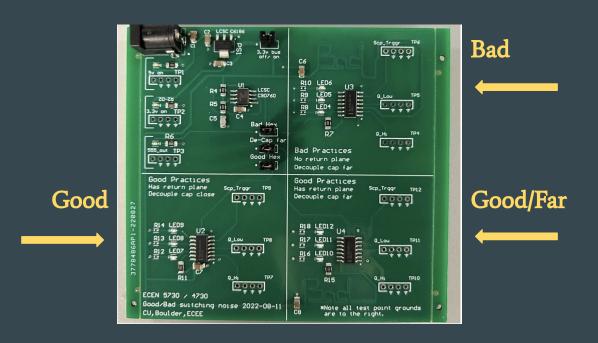

Investigating good vs. bad design on a switching noise board. Specifically, comparing 3 identical circuits but with different layouts.

|                                                        | Rise Time               | Fall Time                       | Voltage Collapse Q_Hi                                                    | Ground Bounce Q_Lo                                                          |

|--------------------------------------------------------|-------------------------|---------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Return Plane w/ Close Decoupling Cap.  GOOD            | ~1.5 ns                 | ~1.3ns                          | <b>0.95 V</b> Rising Edge,<br><b>0.43 V</b> Falling Edge                 | <b>0.45 V</b> Rising Edge,<br><b>0.45 V</b> Falling Edge                    |

| Return Plane w/ Far Decoupling Cap.  GOOD/FAR          | ~3.2 ns<br>(2x slower)* | ~1.4 ns<br>(~same)              | 1.5 V Rising Edge<br>(1.6x worse),<br>2.4 V Falling Edge<br>(5.6x worse) | 0.28 V Rising Edge,<br>(40% better),<br>0.74 V Falling Edge<br>(1.6x worse) |

| No Return Plane w/ Far<br>Decoupling Cap<br><u>BAD</u> | ~3 ns<br>(2x slower)    | ~3.5 ns<br><b>(2.7x slower)</b> | 1.4 V Rising Edge<br>(1.5x worse),<br>2.8 V Falling Edge<br>(6.5x worse) | 0.86 V Rising Edge<br>(2x worse),<br>3.4 V Falling Edge<br>(7.5x worse)     |

<sup>\*</sup>Slower, worse, etc. are in reference to the GOOD design

# Summary

#### Rise/Fall Times:

• The GOOD design had ~2x faster rise times and ~3x faster fall times compared to the BAD design.

#### Voltage Collapse:

- The GOOD design had **50%–85% less voltage collapse** than the BAD design.

- The GOOD/FAR design was significantly worse than GOOD, especially for **voltage collapse (5.6x worse)** .

#### Takeaways:

- Good design practices significantly improve signal integrity —optimized layout reduced rise/fall times by up to 2.7x and minimized voltage collapse on quiet nodes by up to 7.5x , demonstrating the critical impact of proper return paths and proper placement of decoupling capacitors

- Poor layout dramatically increases noise and delays —excessive loop inductance and shared return paths caused longer rise times, severe QHi/QLo voltage collapse (up to 6.5x worse), and greater overall signal degradation

Supporting Data & Measurements

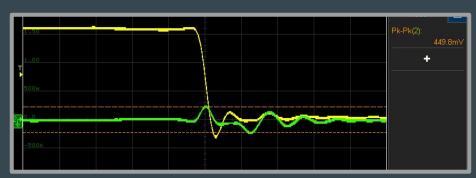

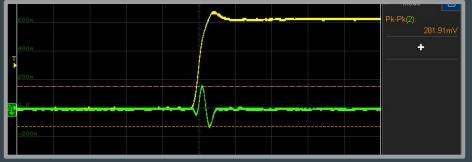

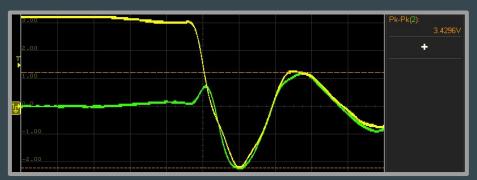

#### Rising Edge

## Falling Edge

Yellow Waveform: GOOD Design (~1.5 ns) Green Waveform: Good/Far Design (~3.2 ns)

Ref Waveform: BAD Design (~3 ns)

GOOD Design (~1.3 ns)

Good/Far Design (~1.4 ns)

BAD Design (~3.5 ns)

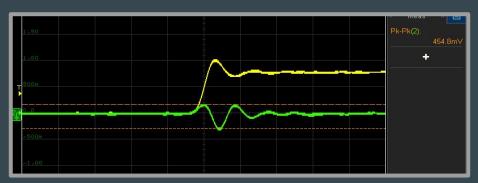

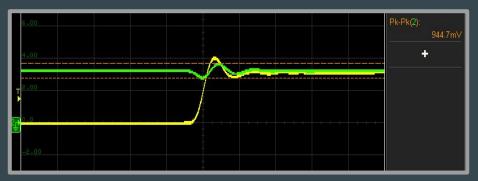

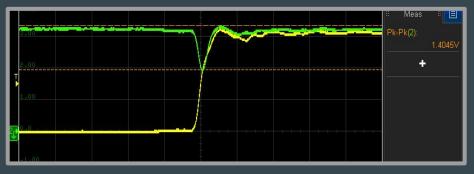

#### **Ground Bounce Quiet Low:**

Falling Edge noise: ~450 mV

Rising Edge noise: ~455 mV

#### **Voltage Collapse Quiet High:**

Falling Edge noise: ~425 mV

Rising Edge noise: ~950 mV

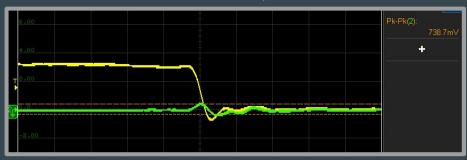

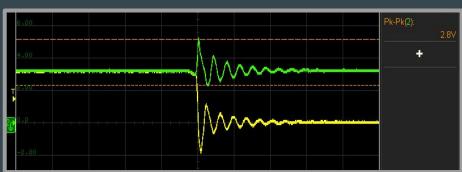

Good/Far Design

### Yellow Waveform: 555 Output trig'd on Edge

Green Waveform: Noise on Rail

#### Ground Bounce Quiet Low:

#### Voltage Collapse Quiet High:

Falling Edge noise: ~740 mV

Falling Edge noise: ~2.4 V

Rising Edge noise: ~282 mV

Rising Edge noise: ~1.5 V

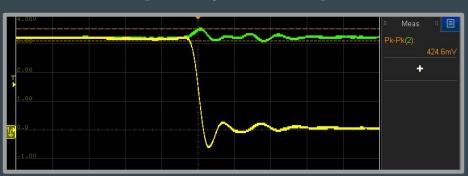

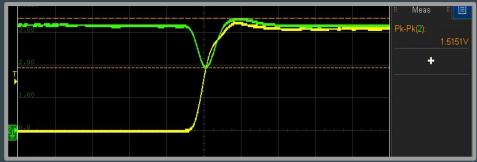

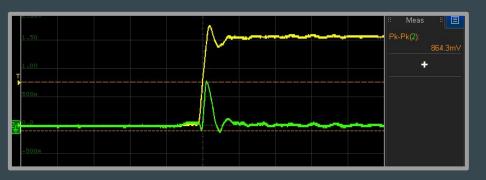

# **BAD Design**

Yellow Waveform: 555 Output trig'd on Edge

Green Waveform: Noise on Rail

#### **Ground Bounce Quiet Low**

Falling Edge noise: ~3.4 V

Rising Edge noise: ~864 mV

#### Voltage Collapse Quiet High:

Falling Edge noise: ~2.8 V

Rising Edge noise: ~1.4 V